# Xilinx VHDL

< Design Suite Version: 14.1>

## **Tutorial**

Department of Electrical and Computer Engineering State University of New York – New Paltz

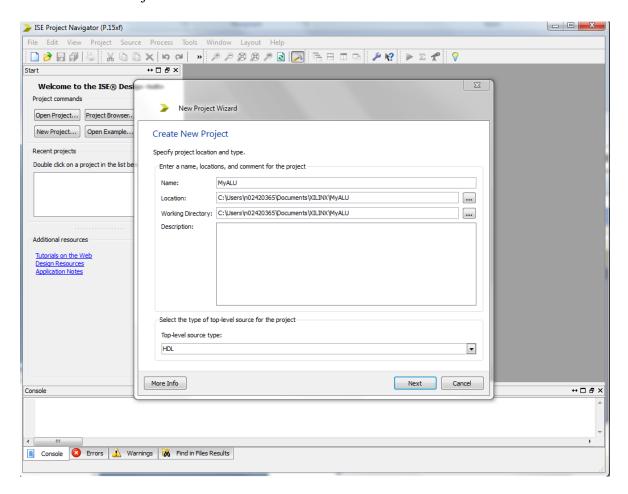

### 1. Start A New Project.

### Click Next.

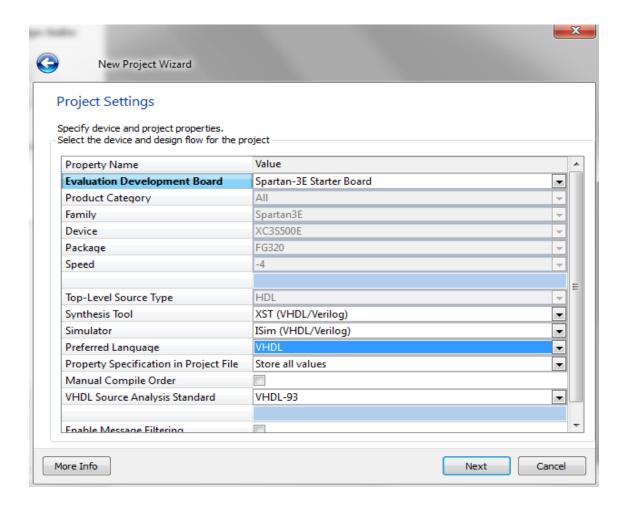

Make Sure the Device Properties are chosen as shown below.

Click Next.

Click finish.

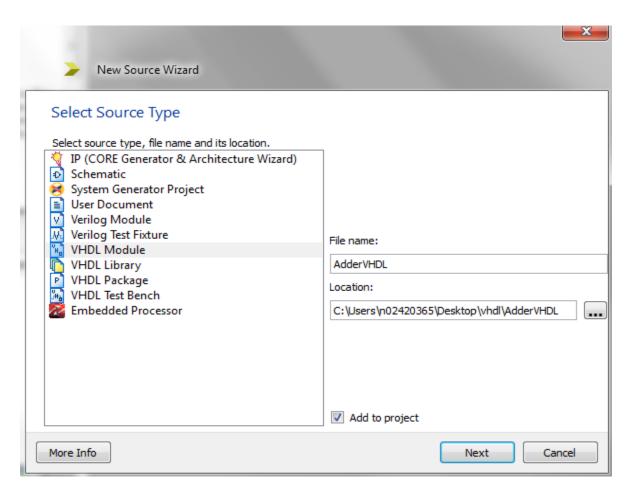

### 2. Go to **Project** <- **New Source**

On the New Source Wizard, click on VHDL module and type a filename.

Click "Next". Click "Finish".

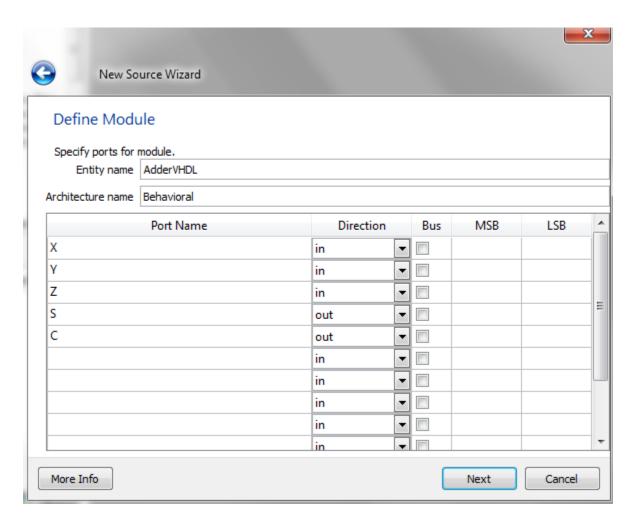

3. In this exercise, you are designing a full adder with X, Y, and Z as inputs and S and C as outputs. Hence, set the ports accordingly.

Click "Next"

Click "Finish"

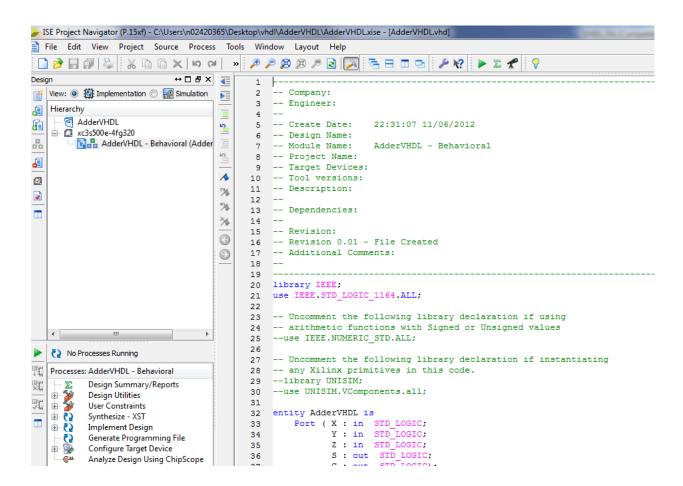

4. This will open the editor where you can input your VHDL code.

Note that

$$S = X \oplus Y \oplus Z$$

$$C = XY + YZ + XZ$$

Hence,

```

library IEEE;

use IEEE STD LOGIC 1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity AdderVHDL is

Port ( X : in STD LOGIC;

Y : in STD LOGIC;

Z : in STD LOGIC;

S : out STD LOGIC;

C : out STD LOGIC);

end AdderVHDL;

architecture Behavioral of AdderVHDL is

begin

S <= X XOR Y XOR Z;

C \leftarrow (X AND Y) OR (Y AND Z) OR (X AND Z);

end Behavioral;

```

5. Save the file.

The project can be simulated using ISE simulator. For ISE simulator details refer the ISE Simulator tutorial.

Make sure that for the **testbench** in the auto generated ".vhd" delete all the clock signal lines(or you can also make them as comments) and follow the same procedure as in the ISE simulator tutorial.

```

60

signal C : std logic;

-- No clocks detected in port list. Replace <clock> below with

61

62

-- appropriate port name

63

64

constant <clock> period : time := 10 ns;

65

BEGIN

66

67

-- Instantiate the Unit Under Test (UUT)

68

uut: AdderVHDL PORT MAP (

69

X => X,

70

Y => Y,

71

72

Z \Rightarrow Z

S => S,

73

C => C

74

75

);

76

77

-- Clock process definitions

<clock>_process :process

78

begin

79

80

<clock> <= '0';

wait for <clock> period/2;

81

82

<clock> <= '1';

wait for <clock>_period/2;

83

end process;

84

85

86

-- Stimulus process

87

88 >

stim_proc: process

89

begin

-- hold reset state for 100 ns.

90

91

wait for 100 ns:

92

93

wait for <clock> period*10;

94

-- insert stimulus here

95

96

wait:

97

98

end process;

99

100 END;

101

```

```

signal testvar : std logic vector (2 downto 0) := "000";

--Outputs

signal S : std logic;

signal C : std logic;

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

--constant <clock> period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: AdderVHDL PORT MAP (

X \Rightarrow X

Y \Rightarrow Y,

Z => Z,

s \Rightarrow s,

C => C

);

-- Clock process definitions

--<clock>_process :process

--begin

--<clock> <= '0';

--wait for <clock> period/2;

--<clock> <= '1';

--wait for <clock> period/2;

--end process;

-- Stimulus process

stim proc: process

begin

-- hold reset state for 100 ns.

--wait for <clock> period*10;

-- insert stimulus here

wait;

end process;

```

When the design is completed, open the User Constraints Editor and assign the pins to the correct inputs and outputs. Follow the steps in the Download Tutorial to complete the process.